cern Editor's note: In this contributed feature, Linda Barney describes the ongoing technical collaboration between CERN and Intel to develop a co-packaged Xeon/FPGA processor.

(http://u=http

fpgAt CERN, the European Organization for Nuclear Research (http://home.cern/about), physicists and engineers are probing the fundamental proces tested ucture of the universe. The Large Hadron Collider (LHC), which began working in 2008, is the world's largest and most powerful particle ataccelerator (http://home.cern/about/how-accelerator-works); it is housed in an underground tunnel at CERN. Niko Neufeld is a deputy project cern early at CERN who works on the Large Hadron Collider beauty (http://lhcb-public.web.cern.ch/lhcb-public/) (LHCb) experiment, which explores what happened after the Big Bang that allowed matter to survive and build the Universe we inhabit today.

(http://ERN experiments produce an enormous amount of data with forty million proton collisions every second, which leads to primary data rates of finitiation for the proton of the pr

uri="DŒRN collaborates with leading ICT companies and other research institutes through a unique public-private partnership known as 'CERN fpgapenlab'. Its goal is to accelerate the development of cutting-edge solutions for the worldwide LHC community and wider scientific research. test@brough a CERN openlab project known as the 'High-Throughput Computing Collaboration,' researchers are investigating the use of various at Intel technologies in data filtering and data acquisition systems.

(http:// url=htt fpgaproces testedatcern%2

(https://6lli539m39y3hpkelqsm3c2fg-wpengine.netdna-ssl.com/wp-content/uploads/2017/04/Fig1-CERN-researchers-LHC-collider-tunnel.jpg)

Figure 1. CERN researchers shown in the Large Hadron Collider tunnel in front of the LHCb detector. Courtesy of CERN (courtesty CERN).

### Introducing the co-packaged Intel CPU / FPGA Processor

Today the CPU and FPGA are used as discrete chips in a solution – with an Intel Xeon processor and an FPGA which is typically attached via a PCIe interconnect to the CPU. And the development environment is also discrete using independent development tools from Intel and tools such as OpenCL and C++. Intel is working toward a common workflow and development flow to better integrate FPGAs.

"FPGA typically uses a higher level machine abstraction language (such as Verilog and VHDL) which have a painful low-level hardware programming model for most people. As a next step, Intel has a solution that co-packages the CPU and FPGA in the same Multichip Chip Product (MCP) package to deliver higher performance and lower latency than a discrete solution," states Bill Jenkins, Intel Senior AI Marketing Manager. The Intel MCP is supported by a cross-platform development framework like OpenCL that can be used to develop applications for both the CPU and FPGA. The Intel solution includes a fully unified intellectual property (IP) and development suite, including languages, libraries and development environments. The roadmap to a unified development flow leverages common tools and libraries to support both FPGA and Intel Xeon processor + FPGA systems along with an expansive ecosystem network of Intel and vendors working on independent development tools for demanding workloads such as HPC, imaging identification, security and big data.

## **Abstracting away FPGA Coding**

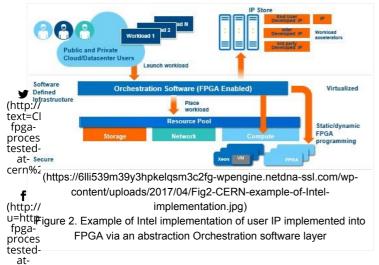

Intel is building an abstraction layer (as part of the product containing the Intel CPU and FPGA in the same MCP package), called the Orchestration Software layer. This layer and the higher level IP and software models help make development less complex so that developers don't need to code specifically to the FPGA. The FPGA-enabled Orchestration software layer abstracts away the API to communicate with the FPGA as shown in the following example.

cern where is a cloud-based library of functions and end-user IP that have been pre-compiled and built that is loaded into the FPGA at runtime. The user first launches a workload from the host and it goes into the Orchestration software which pushes a function into the FPGA. This produces in bitstream that is pre-compiled on the FPGA to bring the data in—it is almost like a fixed architecture I/O interface.

mininthe example scenario, users simply download the image from the abstraction Orchestration software layer to the FPGA and it is ready to run fpganthus for the first indicated in the abstraction of the straction of the abstraction of the straction of the stra

# **G**Large Hadron Collider High-Energy Physics Research at CERN (http://

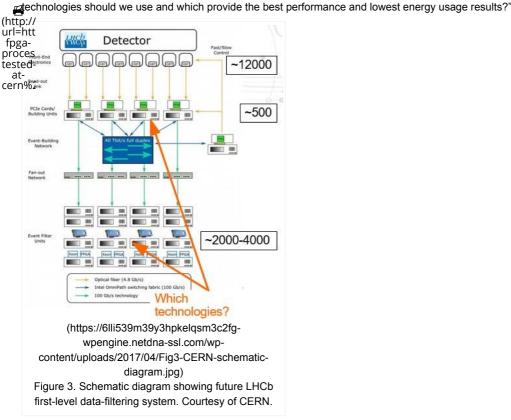

url=Ntufeld indicates that the experiments at CERN — through what they refer to as 'online computing' — require a first-level data-filtering to fpga-proceduce the data to an amount that can be stored and processed on more traditional processing units such as Intel Xeon processors. Figure 3 testedows a schematic view of the future LHCb readout system. At the top level, there is a detector and optical fiber links, which transfer data out of at the detector. CERN uses FPGAs to acquire data from the detector. There are also large switching fabrics, as well as clusters of processing elements including CPUs, FPGAs, and GPUs to reduce the amount of data. One of the questions the CERN team is testing is "Which

**CERN Tests Complex Cherenkov Angle Reconstruction Calculation**

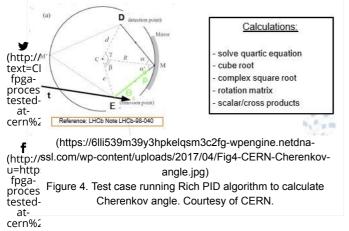

CERN has extensive experience using FPGAs in their research work. "We typically use FPGAs in our research to run algorithms looking for simple integer signatures, or for other less complicated calculations. When we heard about the Intel Xeon / FPGA combined processor, we chose a test using a complex algorithm to do a Cherenkov angle reconstruction of light emission in a particle detector, which is not typically performed on an FPGA. This involves tracing a light particle — photon — through a complex arrangement of optical reflection and deflection systems. Our test case used a rich PID algorithm to calculate the Cherenkov angle for each track and detection point. This is a complex mathematical calculation that involves hyperbolic functions, roots, square roots, etc., as shown in Figure 4. It is one of the most costly calculations done in online reconstruction," states Neufeld.

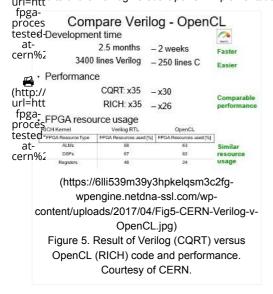

## Coding the Cherenkov Angle Reconstruction in Verilog versus OpenCL

in (http://he CERN team first implemented the Cherenkov angle reconstruction by coding it in the Verilog HDL. The team wrote a 748 clock-cycle long ministpeline in Verilog, along with additional blocks developed for the test including: cubic root, complex square root, rotational matrix, and fpgaross/scalar product. It was a lengthy task doing this coding in Verilog with 3,400 lines of code. With all test benches, the implementation took test@5 months.

atcerrivext, the team recoded the Cherenkov angle code using the OpenCL (https://en.wikipedia.org/wiki/OpenCL)and the BSP (board support

package) designed to work across a variety of hardware platforms. Because OpenCL is an abstraction language, it required only 250 lines of

code and took two weeks of coding. Not only was coding in OpenCL much faster but the performance results were similar. Figure 5 shows the

http://

url=https//

url=https//

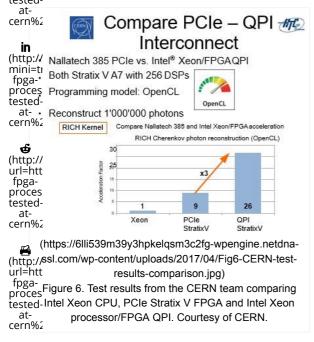

### CERN Compares Co-packaged Intel Xeon - FPGA Processor against Nallatech PCle Stratix V FPGA Board

To test performance of the Verilog code, the CERN team used a commercially available Stratix V GXA7 FPGA board / Nallatech 385 board for testing. They achieved an acceleration of a factor up to six with the Stratix – Nallatech PCle board. However, they found a bottleneck in data transfer—they could not keep the pipeline busy because the PCle card was limited to an eight-lane interface. Next, the CERN team did tests with the Cherenkov angle code comparing a Nallatech FPGA Board with the co-packaged Intel Xeon/FPGA QPI processor.

## **CERN Systems used in Test**

| CENTED VOICENIO ADCA IN 1 COSC                      |                                              |

|-----------------------------------------------------|----------------------------------------------|

| FPGA system used by CERN                            | Intel/FPGA system used by CERN               |

| Nallatech 385 board                                 | Two socket system:                           |

|                                                     | First: Intel® Xeon®E5-2680 v2                |

| FPGA: Altera Stratix V GX A7                        | Second: Intel/Altera Stratix V GX A7 FPGA    |

| • 234'720 ALMs, 940'000 Registers                   | o 234'720 ALMs, 940'000 Registers, 256 DSPs  |

| • 256 DSPs                                          |                                              |

| ♥ Programming model : OpenCL                        | Programming model : Verilog & OpenCL         |

| (http:///<br>text=CHost Interface: 8-lane PCle Gen3 | Host Interface:                              |

| fpga-<br>proces• Up to 7.5GB/s                      | High-bandwidth and low latency               |

| tested Memory: 8GB DDR3 SDRAM                       | Memory: Cache-coherent access to main memory |

| cern%Network Enabled with (2) SFP+ 10GbE ports      |                                              |

(http://u=httpally, the CERN team tested an Intel Xeon CPU, PCIe Stratix V FPGA and Intel Xeon processor/Stratix V QPI (where only the interconnect fpgwas different). As shown in Figure 6, there was a factor of 9 speed up for the PCIe Stratix V FPGA and a 26 factor speed up for the Intel Xeon processor/Stratix V QPI with the faster interconnect.

## CERN Plans to do Future Testing using co-packaged Intel Xeon/ Intel Arria10 FPGA Processor

"Our CERN team found the results of using the co-packaged Intel Xeon processor/Stratix V QPI processors to be very encouraging. In addition, we find the programming model with OpenCL attractive and it will be mandatory for the High-Energy Physics (HEP) field. Intel will be launching a co-packaged Intel Xeon processor / Intel Arria 10 FPGA processor in the future. We want to do other experiments with the co-packaged Intel Xeon processor/ Arria 10 FPGA. We expect that the high-bandwidth interconnect and modern Arria 10 FPGA card will provide high performance and performance per Joule for HEP algorithms," states Neufeld.

Linda Barney is the founder and owner of Barney and Associates, a technical/marketing writing, training and web design firm in Beaverton, OR.

### Subscribe to HPCwire's Weekly Update!

Be the most informed person in the room! Stay ahead of the tech trends with industy updates delivered to you every week!

● EDITOR'S PICKS

**●** MOST POPULAR

◆ THE LATEST

(https://www.hpcwire.com/subscribe/)

More Career Resources > (http://careers.hpcwire.com)

## Facebook Open Sources Caffe2; Nvidia, Intel Rush to Optimize

(https://www.hpcwire.com/2017/04/18/facebook-open-sources-caffe2-nvidia-intel-jumpstart-optimizations/)

From its F8 developer conference in San Jose, Calif., today, Facebook announced Caffe2, a new open-source, cross-platform framework for deep learning. Caffe2 is to Caffe, the deep learning framework developed by Berkeley Al Research and community contributors. Read more... (https://www.hpcwire.com/2017/04/18/facebook caffe2-nvidia-intel-jumpstart-optimizations/)

By Tiffany Trader

status=Facebook+Open+Sources+Caffe2%3B+Nvidia%2C+Intel+Rush+to+Optimize+https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F18% open-sources-caffe2-nvidia-intel-jumpstart-optimizations%2F) **in** (http://www.linkedin.com/shareArticle?

mini=true&url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F18%2Ffacebook-open-sources-caffe2-nvidia-intel-jumpstart-

optimizations%2F&title=Facebook+Open+Sources+Caffe2%3B+Nvidia%2C+Intel+Rush+to+Optimize&source=https%3A%2F%2Fwww.hpcwire.com (http://www.facebook.com/sharer/sharer.php?u=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F18%2Ffacebook-open-sources-caffe2-nvi jumpstart-optimizations%2F&title=Facebook+Open+Sources+Caffe2%3B+Nvidia%2C+Intel+Rush+to+Optimize/) G+ (https://plus.google.com/share/https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F18%2Ffacebook-open-sources-caffe2-nvidia-intel-jumpstart-optimizations%2F)

### in (http://nights Landing Processor with Omni-Path Makes Cloud Debut

min(https://www.hpcwire.com/2017/04/18/knights-landing-processor-omni-path-makes-cloud-debut/) fpga-

tested cloud specialist Rescale is partnering with Intel and HPC resource provider R Systems to offer first-ever cloud access to Xeon Phi "Knights Landing" processors. atinfrastructure is based on the 68-core Intel Knights Landing processor with integrated Omni-Path fabric (the 7250F Xeon Phi). Read more... cerr/##fps://www.hpcwire.com/2017/04/18/knights-landing-processor-omni-path-makes-cloud-debut/)

By Tiffany Trader

cern%2

(http://twitter.com/intent/tweet?status=Knights+Landing+Processor+with+Omni-

url=PEth+Makes+Cloud+Debut+https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F18%2Fknights-landing-processor-omni-path-makes-cloud-de fpga-prodetp://www.linkedin.com/shareArticle?mini=true&url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F18%2Fknights-landing-processor-om testemakes-cloud-debut%2F&title=Knights+Landing+Processor+with+Omni-Path+Makes+Cloud+Debut&source=https%3A%2F%2Fwww.hpcwire.com/) attacked the complete of the complet

#url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F18%2Fknights-landing-processor-omni-path-makes-cloud-debut%2F

## **IBM Coils Anaconda Around Power Processor**

(https://www.hpcwire.com/2017/04/17/ibm-coils-anaconda-around-power-processor/)

IBM, which recently extended support for the Anaconda data science platform to its open source mainframe, takes another step this week by offering the data platform Cognitive Systems platform in collaboration with Anaconda developer Continuum Analytics. Read more... (https://www.hpcwire.com/2017/04/17/ibm-coils-anaconda-a processor/)

By George Leopold

status=IBM+Coils+Anaconda+Around+Power+Processor+https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F17%2Fibm-coils-anaconda-aro processor%2F) in (http://www.linkedin.com/shareArticle?mini=true&url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F17%2Fibm-coils

around-power-processor%2F&title=IBM+Coils+Anaconda+Around+Power+Processor&source=https%3A%2F%2Fwww.hpcwire.com/) **f** (http://www.facebook.com/sharer/sharer.php?u=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F17%2Fibm-coils-anaconda-around-power processor%2F&title=IBM+Coils+Anaconda+Around+Power+Processor/) **G+** (https://plus.google.com/share? url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F17%2Fibm-coils-anaconda-around-power-processor%2F)

## (http://ERN openlab Explores New CPU/FPGA Processing Solutions

fpgg https://www.hpcwire.com/2017/04/14/xeon-fpga-processor-tested-at-cern/)

proces

tested rough a CERN openlab project known as the 'High-Throughput Computing Collaboration,' researchers are investigating the use of various Intel technologies in data at data acquisition systems. Read more... (https://www.hpcwire.com/2017/04/14/xeon-fpga-processor-tested-at-cern/) cern %2

By Linda Barney

f y (http://twitter.com/intent/tweet?

${\tt cern} \& {\tt fn} \& {\tt 2F\&title=CERN+openlab+Explores+New+CPU} \& {\tt 2FFPGA+Processing+Solutions/}) \ \ {\tt G+} \ \ ({\tt https://plus.google.com/share?}) \ \ {\tt cern} \& {\tt fn} \& {\tt 2F\&title=CERN+openlab+Explores+New+CPU} \& {\tt 2FFPGA+Processing+Solutions/}) \ \ {\tt G+} \ \ ({\tt https://plus.google.com/share?}) \ \ {\tt cern} \& {\tt fn} \& {$

in url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F14%2Fxeon-fpga-processor-tested-at-cern%2F)

(http:// mini=ti

## fpgHPE Extreme Performance Solutions

(http://pc-Driven Weather Simulations Improving Forecasting Capabilities

fpg(https://www.hpcwire.com/solution\_content/hpe/weather-climate/hpc-driven-weather-simulations-improvingprocesting-capabilities/)

at In September of 1938, a massive hurricane (http://sos.ri.gov/virtualarchives/items/show/291) traversed the Atlantic Ocean and made landfall in New England. Due to in Cerning prect forecasting, the storm struck farther north and with greater intensity than had been predicted, leaving residents and authorities with virtually no warning or time prepare. Read more... (https://www.hpcwire.com/solution\_content/hpe/weather-climate/hpc-driven-weather-simulations-improving-forecasting-capabilities/)

Visit the

(https://www.hpcwire.com/solution\_channel/hpe/)

- Al and Deep Learning Come to Wall Street (https://www.hpcwire.com/solution\_content/hpe/financial-services/ai-deep-learning-come-wall-street/)

- Enhancing the Speed and Security of Energy Production with Remote Visualization (https://www.hpcwire.com/solution\_content/hpe/energy-oil-gas/enhancing-speed energy-production-remote-visualization/)

- HPE Servers Demonstrate Critical Speed for HFT Traders on STAC-N1 Test (https://www.hpcwire.com/solution\_content/hpe/financial-services/hpe-servers-demons/speed-hft-traders-stac-n1-test/)

## **DOE Supercomputer Achieves Record 45-Qubit Quantum Simulation**

(https://www.hpcwire.com/2017/04/13/doe-supercomputer-45-qubit-quantum-computer/)

In order to simulate larger and larger quantum systems and usher in an age of "quantum supremacy," Read more... (https://www.hpcwire.com/2017/04/13/doe-supercqubit-quantum-computer/)

By Tiffany Trader

★ (http://twitter.com/intent/tweet?status=DOE+Supercomputer+Achieves+Record+45-

Qubit+Quantum+Simulation+https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F13%2Fdoe-supercomputer-45-qubit-quantum-computer%2F (http://www.linkedin.com/shareArticle?mini=true&url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F13%2Fdoe-supercomputer-45-qubit-computer%2F&title=DOE+Supercomputer+Achieves+Record+45-Qubit+Quantum+Simulation&source=https%3A%2F%2Fwww.hpcwire.com/) **f** (http://www.facebook.com/sharer/sharer.php?u=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F13%2Fdoe-supercomputer-45-qubit-quantum+Simulation/) **G+** (https://plus.google.com/share?

(http://=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F13%2Fdoe-supercomputer-45-qubit-quantum-computer%2F)

## in Hyperscalers Emerging From 'Hype Phase

mini#fips://www.hpcwire.com/2017/04/12/hyperscalers-emerging-hype-phase/) fpga-

proces number of companies fitting the description of "hyperscale" now accounts for 68 percent of the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found. Read more tested in the cloud infrastructure services market, a researcher found.

cerns/j2George Leopold

(http://twitter.com/intent/tweet?

status=Hyperscalers+Emerging+From+%E2%80%98Hype+Phase%E2%80%99+https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F12%2Ftwr!=#merging-hype-phase%2F) in (http://www.linkedin.com/shareArticle?

fpganini=true&url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F12%2Fhyperscalers-emerging-hype-

tested ase%2F&title=Hyperscalers+Emerging+From+%E2%80%98Hype+Phase%E2%80%99&source=https%3A%2F%2Fwww.hpcwire.com/)

at(http://www.facebook.com/sharer/sharer.php?u=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F12%2Fhyperscalers-emerging-hype-cern%2F2017%2F04%2F12%2Fhyperscalers-emerging-hype-phase%2F&title=Hyperscalers+Emerging+From+%E2%80%98Hype+Phase%E2%80%99/) G+ (https://plus.google.com/share?

url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F12%2Fhyperscalers-emerging-hype-phase%2F)

## Penguin Takes a Run at the Big Cloud Providers

(https://www.hpcwire.com/2017/04/12/penguin-takes-run-big-cloud-providers/)

HPC specialist Penguin Computing recently re-ran benchmarks from a study of its larger brethren and says the results show its 'public cloud' – Penguin on Demand (Famong the leaders in cost and performance. Read more... (https://www.hpcwire.com/2017/04/12/penguin-takes-run-big-cloud-providers/)

By John Russell

cloud-providers%2F&title=Penguin+Takes+a+Run+at+the+Big+Cloud+Providers&source=https%3A%2F%2Fwww.hpcwire.com/) **f** (http://www.facebook.com/sharer/sharer.php?u=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F12%2Fpenguin-takes-run-big-cloud-providers%2F&title=Penguin+Takes+a+Run+at+the+Big+Cloud+Providers/) **G+** (https://plus.google.com/share? url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F12%2Fpenguin-takes-run-big-cloud-providers%2F)

## (http://pin Claims Faster Object Storage 'Cross-Region' S3 Connectivity than AWS

fpgd/https://www.hpcwire.com/2017/04/11/ddn-claims-faster-object-storage-cross-region-s3-connectivity-aws/) proces

tested vanced-scale storage specialist DataDirect Networks (DDN), whose solutions populate the upper-rung of the Top500 supercomputing list, today announced new "cr at features to its WOS object storage platform that support multi-site AWS connectivity as well as new data protection and disaster recovery capabilities. Read more... cerr/inteps://www.hpcwire.com/2017/04/11/ddn-claims-faster-object-storage-cross-region-s3-connectivity-aws/)

#### **\_**By Doug Black

proces testedatcern%2

(http:// url=htt

fpgaproces

testedatcern%2

(http:// url=htt fpga-

proces tested

atcern%2

(http://twitter.com/intent/tweet?status=DDN+Claims+Faster+Object+Storage+%E2%80%98Cross-

u=https://onectivity-than+AWS+https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F11%2Fddn-claims-faster-object-storage-gion-s3-connectivity-aws%2F) in (http://www.linkedin.com/shareArticle?mini=true&url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2test@fims-faster-object-storage-cross-region-s3-connectivity-aws%2F&title=DDN+Claims+Faster+Object+Storage+%E2%80%98Cross-

carribegion%E2%80%99+S3+Connectivity+than+AWS&source=https%3A%2F%2Fwww.hpcwire.com/) **f** (http://www.facebook.com/sharer/sharer.phpu=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F11%2Fddn-claims-faster-object-storage-cross-region-s3-connectivity-

inaws%2F&title=DDN+Claims+Faster+Object+Storage+%E2%80%98Cross-Region%E2%80%99+S3+Connectivity+than+AWS/) G+

(http://plus.google.com/share?url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F11%2Fddn-claims-faster-object-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storage-cross-region-storag

Leading Solution Providers applied (http://tci.taborcommunications.com/APM) Altair (http://tci.taborcommunications.com/sponsor-altair-2 (http://tci.taborcommunications.com/sponsor-aspen) ASETEK (http://tci.taborcommunications.com/sponsor-asetek 🆚 (http://tci.taborcommunications.com/sponsor-atipa) (http://tci.taborcommunications.com/sponsor-asrock /ISReck (http://tci.taborcommunications.com/sponsor-bull) (http://tci.taborcommunications.com/sponsor-cray) (http://tci.taborcommunications.com/sponsor-ddn Chttp://tci.taborcommunications.com/sponsor-dell (http://tci.taborcommunications.com/l/21812/2016-07-28/5fzz61 ett Packard (http://tci.taborcommunications.com/sponsor-hp-3) (http://tci.taborcommunications.com/sponsor-ibm) **INSPUT** (http://tci.taborcommunications.com/sponsor-inspur (intel) (http://tci.taborcommunications.com/sponsor-intel) (http://tci.taborcommunications.com/sponsor-lenovo Mellanox (http://tci.taborcommunications.com/sponsor-mellanox) Microsoft (http://tci.taborcommunications.com/sponsor-microsoft) NEC (http://tci.taborcommunications.com/sponsor-nec) PENGUIN (http://tci.taborcommunications.com/l/21812/2014-04-25/5l3mh) (http://tci.taborcommunications.com/sponsor-pgi (http://tci.taborcommunications.com/sponsor-PSSCLabs) (http://tci.taborcommunications.com/sponsor-purestorage (http://tci.taborcommunications.com/re-store-2) (http://tci.taborcommunications.com/sponsor-Seagate-2) (http://tci.taborcommunications.com/sponsor-sgi) (http://tci.taborcommunications.com/sponsor-supermicro) (http://tci.taborcommunications.com/verneglobal)

## cern butch Researchers Build Little Green Machine II Out of IBM Minsky Servers

(https://www.hpcwire.com/2017/04/11/dutch-uni-builds-little-green-machine-ii-out-of-ibm-minsky-servers/)

(http://

min Fite newest Dutch HPC cluster is only four "pizza boxes" high, small enough to be carried around on a bicycle, but Little Green Machine II, as the new system is called fpgæsearch in oceanography, computer science, artificial intelligence, financial modeling and astronomy. Read more... (https://www.hpcwire.com/2017/04/11/dutch-uni-b procest-of-ibm-minsky-servers/)

tested-atBy Tiffany Trader

cern% (http://twitter.com/intent/tweet?

.status=Dutch+Researchers+Build+Little+Green+Machine+II+Out+of+IBM+Minsky+Servers+https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04% (http://lds-little-green-machine-ii-out-of-ibm-minsky-servers%2F) in (http://www.linkedin.com/shareArticle?

url=httni=true&url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F11%2Fdutch-uni-builds-little-green-machine-ii-out-of-ibm-minskyfpggervers%2F&title=Dutch+Researchers+Build+Little+Green+Machine+II+Out+of+IBM+Minsky+Servers&source=https%3A%2F%2Fwww.hpcwire.con procests: http://www.facebook.com/sharer/sharer.php?u=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F11%2Fdutch-uni-builds-little-green-machi atservers%2F&title=Dutch+Researchers+Build+Little+Green+Machine+II+Out+of+IBM+Minsky+Servers/) G+ (https://plus.google.com/share? cern%2 url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F11%2Fdutch-uni-builds-little-green-machine-ii-out-of-ibm-minsky-servers%2F)

(http:// url=htt fpgaproces testedat-cern%2

## <sup>fpg</sup>୍ଲMU's Latest Poker Program Wins in China

test editps://www.hpcwire.com/2017/04/11/cmus-latest-poker-program-wins-china/)

Cern of now become old hat – Al poker algorithm beats humans. Carnegie Mellon University is at the forefront of creating this new class of crafty Al gamblers. Read more. (https://www.hpcwire.com/2017/04/11/cmus-latest-poker-program-wins-china/)

By John Russell

###

china%2F&title=CMU%E2%80%99s+Latest+Poker+Program+Wins+in+China&source=https%3A%2F%2Fwww.hpcwire.com/) **f**(http://www.facebook.com/sharer/sharer.php?u=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F11%2Fcmus-latest-poker-program-wins-china%2F&title=CMU%E2%80%99s+Latest+Poker+Program+Wins+in+China/) **G+** (https://plus.google.com/share? url=https%3A%2F%2Fwww.hpcwire.com%2F2017%2F04%2F11%2Fcmus-latest-poker-program-wins-china%2F)